新闻资讯

News

20

2025

-

07

索尼开发新款三层堆叠式CMOS图像传感器,多项性能有望大幅提升

作者:

据麦姆斯咨询报道,索尼(Sony)成像和传感解决方案 (I&SS) 部门最近与投资者进行了一次交流会谈,在主题演讲环节,索尼详细介绍了一种有望显著提高性能的前瞻性三层堆叠式CMOS图像传感器(CIS)。

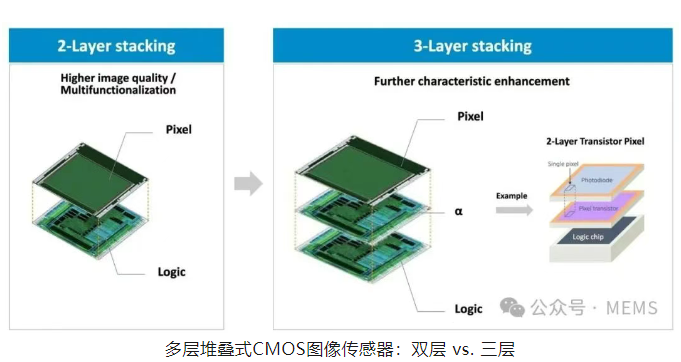

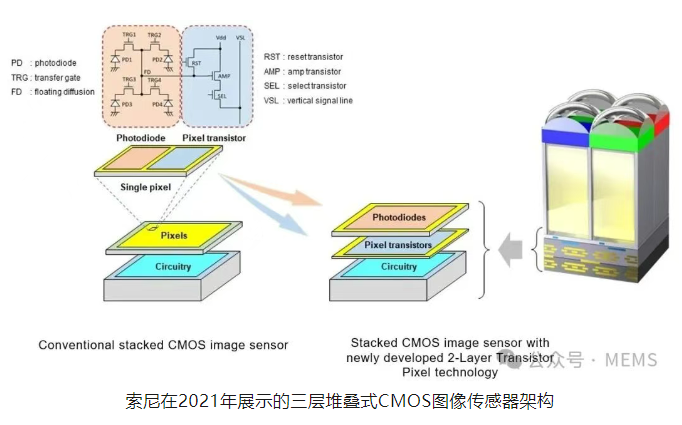

作为长期目标的一部分,索尼正在大力投资新的CMOS图像传感器技术,包括改进的多层堆叠式CMOS图像传感器。索尼已在旗舰智能手机的多款摄像头中使用堆叠式CMOS图像传感器,但这些图像传感器是双层的:其中一层是光电二极管层,包含用于感光的像素阵列;另一层是位于下方的逻辑电路层,负责图像处理任务。

索尼长期致力于在堆叠式CMOS图像传感器中增加第三层,这实际上意味着扩展图像处理能力并提升成像质量。在其它条件相同的情况下,通常,传感器级别的处理能力越强越好。

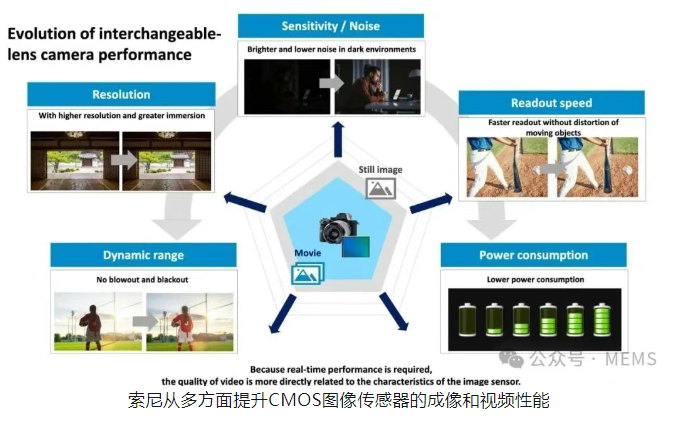

增强传感器级别的处理能力可以提升动态范围、灵敏度、噪声、效率、读取速度和分辨率,最后一个优势更多地体现在视频性能上,而非静态图像。增加新的传感器层本身并不会改变分辨率,但通过提高传感器的速度和性能,可以解锁新的视频录制模式。目前,高分辨率CMOS图像传感器的视频分辨率通常受到处理瓶颈的限制,因此,突破该瓶颈可以进一步提升视频性能。

更快的读出速度几乎对摄像头性能的各个方面都至关重要,包括卷帘快门、连拍速度和自动对焦性能。

动态范围方面的提升颇为复杂。更好的传感器级别图像处理可以提升动态范围,但是CMOS图像传感器的实际动态范围取决于许多因素,包括传感器像素的满阱容量和传感器级别的噪声性能。虽然图像处理会优化噪声,但满阱容量是实际像素的物理状态,在传感器上添加更多层实际上会通过物理缩小像素使得满阱容量降低。

然而,索尼早在2021年发布三层堆叠式CMOS图像传感器的初始概念时就解释了这种情况。正如索尼之前所演示的那样,增加的第三层也可以是位于光电二极管层下方的像素晶体管层,而不是第二个纯处理层。

三层堆叠式CMOS图像传感器何时能应用于索尼的消费类终端产品仍是一个未知数,但索尼已经一次又一次地证明,其能够制造出突破性的CMOS图像传感器,例如索尼全画幅无反相机a9 III(A9M3)中采用的全局快门CMOS图像传感器,以及a1系列相机中采用的快速高分辨率堆叠式CMOS图像传感器。索尼仍然致力于全画幅CMOS图像传感器的开发,未来前景光明。

上一条

下一条

上一条

下一条

最新动态

感谢您访问崇帆科技官方网站,如有合作意向或建议,请通过以下方式联系我们,我们会尽快给予回复,谢谢!

移动版

官方公众号